# 06 - Esercizio progetto su 8088

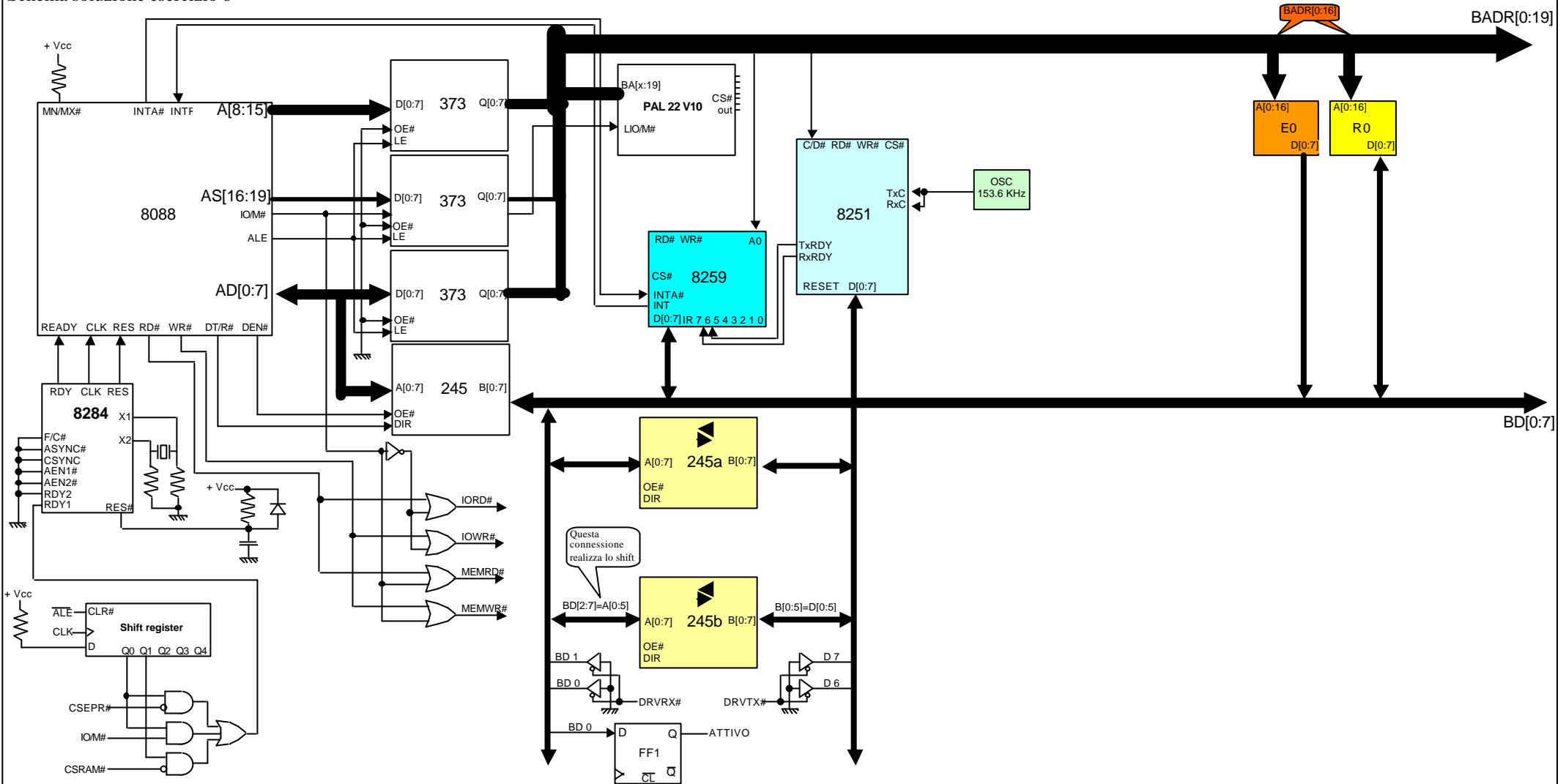

Un sistema a microprocessore basato su 8088 a 5 MHz dispone di 128KB di Eprom (Tacc = 100 nsec) agli indirizzi alti e 128KB di Ram (Tacc = 0.41 $\mu$ sec) agli indirizzi bassi.

Il sistema dispone di un'interfaccia seriale 8251 (9600 baud, parità pari, 8 bit dato, 1 stop bit, divisore interno a 16X) gestito a interruzione in grado di scambiare dati con una periferica esterna.

Si vuole realizzare un dispositivo attivabile e disattivabile via software in grado di dividere per 4 tutti e soli i dati trasmessi e moltiplicare per 4 tutti e soli i dati ricevuti. Una volta attivate, la moltiplicazione e la divisione devono avvenire in modo trasparente al microprocessore. Si assuma che, con tale dispositivo in funzione, i dati ricevuti abbiano valore minore o uguale a 3FH mentre quelli trasmessi siano tutti multipli di 4.

1- Disegnare lo schema di sistema nell'ipotesi che le periferiche di I/O non richiedano TW e considerando il Tacc come "caso peggiore" nel calcolo dei TW richiesti dalle memorie.

2- Scrivere le espressioni di selezione semplificate delle memorie e dei dispositivi.

3- Progettare il dispositivo richiesto cercando di ottimizzarlo il più possibile.

## SOLUZIONE dell'esercizio 6

### Principi generali del progetto proposto

Dividere e moltiplicare un numero binario per un numero pari consiste rispettivamente nello shiftare a destra e a sinistra il numero di partenza per un numero di posizioni pari alla potenza del 2 del dividendo. Così, ad esempio, dividere per 4 significa shiftare la stringa di due posizioni a destra. Esaminando quanto richiesto ci si accorgerà che dividere per 4 un flusso di dati equivale a moltiplicare per 4 il flusso del senso contrario, il ché rende la connessione identica nei due casi, con l'unica eccezione che bisognerà aver cura di non lasciare in 3-state le linee BD[0,1] del bus dati durante la ricezione e le linee dato D[6,7] dell'8251 durante la trasmissione. E' opportuno anche notare che i driving delle suddette linee con "zero" logici devono essere attivi alternativamente per non cortocircuitare a massa le linee in presenza di altri segnali di pilotaggio (del BD in trasmissione e dell'8251 in ricezione). Per consentire al  $\mu$ P di attivare il circuito divosore/moltiplicatore mapperemo un FFD (FF1) nello spazio di I/O. Altrettanto faremo con FF2 per campionare il bit 6 dei caratteri ricevuti e memorizzare se almeno uno di questi avesse superato la soglia 3FH.

Lo shift di divisione/moltiplicazione è implementato nel collegamento tra il bus dati ed il gate "A" del transceiver 245b. Quando il circuito è inattivo funziona il 245a e si spegne il 245b.

### Calcolo dei TW per le memorie

Supponendo un sufficiente anticipo nell'attivazione del segnale MEMRD\* tale da rendere influente solo il parametro Tacc si ha:

$$T_{clcl} = 200 \text{ nsec}$$

$$T_{accEeprom} = 100 \text{ nsec}$$

$$TDV = T_{clavmax}(110 \text{ nsec}@5MHz) + T_{373}(18 \text{ nsec}) + T_{pal}(30 \text{ nsec}) + T_{accEeprom}(100 \text{ nsec}) + T_{245}(10 \text{ nsec}) + T_{dvclmin}(30 \text{ nsec}@5MHz) = 298 \text{ nsec}$$

$$TDV \leq (3+n) \cdot T_{clcl} \Rightarrow \text{per } n=0 \text{ è verificata } (298 \leq 600) \Rightarrow \underline{0 \text{ TWait per i chip di Eeprom}}$$

$$T_{accRam} = 410 \text{ nsec}$$

$$TDV = T_{clavmax}(110 \text{ nsec}@5MHz) + T_{373}(18 \text{ nsec}) + T_{pal}(30 \text{ nsec}) + T_{accRam}(410 \text{ nsec}) + T_{245}(10 \text{ nsec}) + T_{dvclmin}(30 \text{ nsec}@5MHz) = 608 \text{ nsec}$$

$$TDV \leq (3+n) \cdot T_{clcl} \Rightarrow \text{per } n=0 \text{ si ha } (608 > 600) \Rightarrow \text{non è verificata} \Rightarrow \\ \text{per } n=1 \Rightarrow (608 \leq 800) \Rightarrow \text{è verificata} \Rightarrow \underline{1 \text{ TWait per il chip di Ram.}}$$

### Sintesi dei segnali

Selezione memorie:

$$CSE0 = BA19 \cdot \text{!IO/M\#}$$

$$CSR0 = \text{!BA19} \cdot \text{!IO/M\#}$$

Selezione delle periferiche:

$$CS8251 = \text{!BA15} \cdot \text{!BA14} \cdot \text{IO/M\#}$$

$$CS8259 = \text{!BA15} \cdot \text{BA14} \cdot \text{IO/M\#}$$

$$CSFF1 = BA15 \cdot \text{!BA14} \cdot \text{IO/M\#}$$

Segnali di controllo:

$$\begin{array}{ll} DIR245a = DT/R\# & OE245a\# = \text{ATTIVO} \\ DIR245b = DT/R\# & OE245b\# = \text{!ATTIVO} \end{array}$$

$$\begin{array}{ll} DRVRX\# = \text{!CS8251} + \text{IORD\#} + BA0 + \text{!ATTIVO} \\ DRVTRX\# = \text{!CS8251} + \text{IOWR\#} + BA0 + \text{!ATTIVO} \end{array}$$

$$CKFF1 = \text{!CSFF1} + \text{IOWR\#}$$

$$CLFF1\# = \text{BRDRES\#}$$

Schema soluzione esercizio 6