| Nome Cognome | Matricola |

|--------------|-----------|

|              |           |

# Calcolatori Elettronici L A Prova scritta del 26/9/'03

## Esercizio N. 1 (12 punti)

Sia data la seguente porzione di codice assembler per una CPU di tipo DLX:

SUB R5, R7, R9

SUB R4, R6, R8

AND R1, R11, R5

- 1.1) tracciare il diagramma clock/stadi supponendo che una Hazard Detection Unit introduca tutti gli stalli necessari a risolvere le alee; (3 punti)

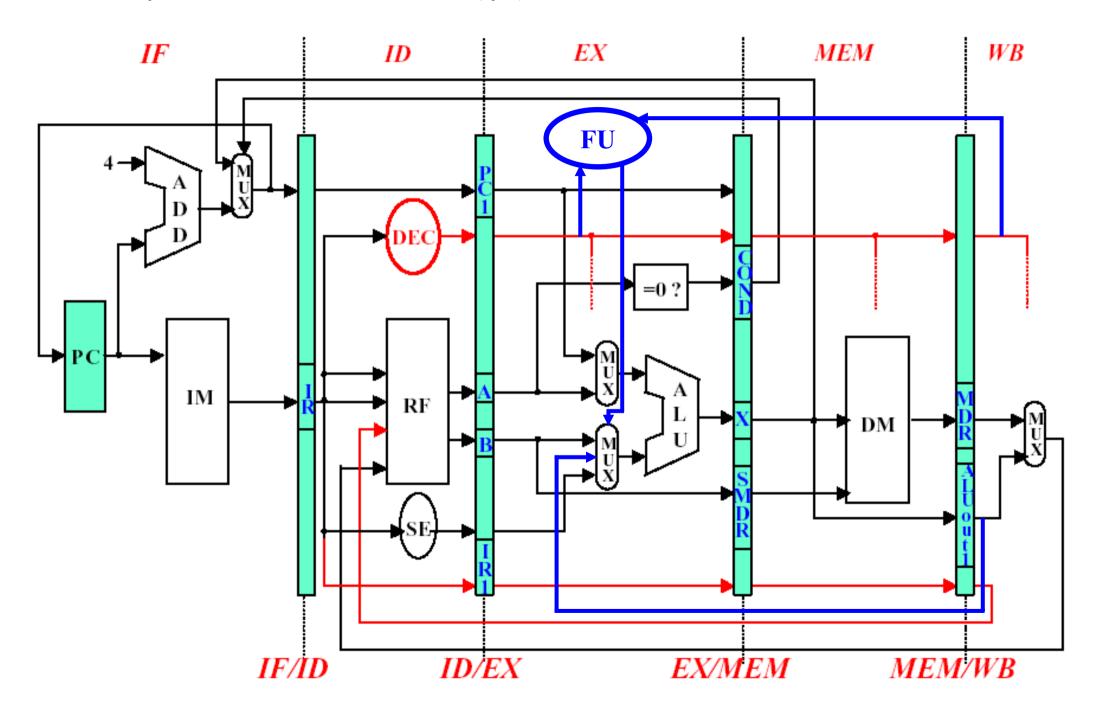

- 1.2) disegnare lo schema del datapath (senza HDU) progettando una Forwarding Unit in grado di ridurre al massimo gli stalli di pipeline, avendo cura di specificare quali segnali in ingresso siano necessari alla FU; (3 punti)

- 1.3) descrivere a parole il funzionamento della FU progettata, spiegando quali debbano essere i dati in ingresso e come debba comportarsi la FU in funzione del loro contenuto; (4 punti)

- 1.4) tracciare il nuovo diagramma clock/stadi che tiene conto del forwarding realizzato; (2 punti)

### Esercizio N. 2 (12 punti)

Un sistema a microprocessore basato su 8088 a 5 MHz dispone di 32KB di Eprom (1 chip agli indirizzi alti) e 256KB di Ram (1 chip agli indirizzi bassi).

Si vuole interfacciare al sistema una periferica di misura esterna "EXT" che dispone di una connessione standard di tipo RS-232, e di un bus parallelo a 8 bit avente caratteristiche in tutto compatibili con quelle del bus del nostro sistema. Trasmettendo il carattere 55H sulla linea RS-232, la periferica "EXT" notifica la disponibilità a fornire un numero imprecisato di caratteri precedentemente accumulati nelle ripetute letture di un trasduttore in essa contenuto. Il bus parallelo a 8 bit serve per far leggere al µP i caratteri accumulati: dopo aver trasmesso 55H su RS-232, la periferica è pronta a rilasciare un nuovo carattere sul bus parallelo ogni volta che si attivano assieme i suoi ingressi di selezione CSEXT# e di output enable OEXT#. Quando la periferica ha esaurito i caratteri accumulati lo notifica effettuando la trasmissione su RS-232 del carattere 0FH. La trasmissione dei caratteri 55H avviene con una cadenza approssimativa di uno al minuto.

- 2.1) Progettare il circuito per la generazione del segnale di READY nell'ipotesi che soltanto la periferica EXT necessiti di 2 periodi di wait. (2 punti)

- 2.2) Disegnare lo schema che mostra come si intende interfacciare la periferica al bus di sistema, aggiungendo i dispositivi di interfacciamento che si ritengono necessari; descrivere in breve le caratteristiche dell'interfacciamento giustificandone le scelte. (8 punti)

- 2.3) Scrivere le espressioni di selezione <u>semplificate</u> delle memorie e dei dispositivi di I/O. (2 punti)

#### Esercizio N. 3 (9 punti)

- 3.1) Dal momento in cui viene fornita tensione al componente 8251, cos'è necessario fare affinché esso diventi pronto a scambiare dati tra il µP e la linea seriale? (3 punti)

- 3.2) Dire quanti segmenti diversi è possibile indirizzare nello spazio di memoria di un'ISA iA16 su 8088 e dire se tutti i segmenti indirizzabili hanno la stessa quantità di celle realmente accessibili. (4 punti)

- 3.3) Dire se nell'ISA iA16 vi sono istruzioni che consentono operazioni tra due operandi in memoria ed, in base alla risposta, classificare l'ISA rispetto al tipo di operandi sui quali un'istruzione assembler può compiere operazioni. (2 punti)

Durante il compito non si può uscire dopo le ore 11:00 Consegnando un elaborato per la correzione decade la validità del voto precedente Correzione e registrazione il 3/10/03, ore 10:00 Via Rasi

### SOLUZIONE del compito di Calcolatori Elettronici L A del 26/9/'03

1.1) (3 punti) Diagramma clock/stadi con gli stalli

| SUB R5, R7, R9  |  |

|-----------------|--|

| SUB R4, R6, R8  |  |

| AND R1, R11, R5 |  |

|   | ck1 | ck2 | ck3 | ck4 | ck5 | ck6 | ck7 | ck8 | ck9 |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Ī | IF  | ID  | EX  | MEM | WB  |     |     |     |     |

| Ī |     | IF  | ID  | EX  | MEM | WB  |     |     |     |

|   |     |     | F   | S   | S   | ID  | EX  | MEM | WB  |

La HDU del DLX introduce gli stalli quando si rende necessario il decode della AND il cui operando sorgente R5 è anche il registro destinazione della prima SUB che in quell'istante è nello stadio MEM. Tale condizione di alea

permane finché non si è completato il WB della prima SUB, dopodiché la AND può procedere in pipeline.

- 1.2) (3 punti) Per lo schema del progetto della FU si veda la prossima pagina.

- **1.3)** (4 punti) La Forwarding Unit progettata deve essere in grado di riconoscere se negli stadi EX e WB sono contemporaneamente presenti due istruzioni di tipo ALU delle quali quella in EX necessiti di un dato che corrisponde al risultato di quella che nello stesso istante si trova in WB. Per questo motivo all'ingresso della FU devono arrivare i codici operativi delle istruzioni presenti nei due stadi suddetti. La FU si occuperà di identificare il codice operativo di una tra le possibili istruzioni ALU presenti nei due stadi (nel nostro caso SUB e AND) e controllerà se uno dei due registri sorgente della istruzione in EX corrisponda al registro destinazione dell'istruzione in WB: in tal caso comanderà al MUX posto sull'ingresso della ALU di commutare sul ramo derivato dall'uscita del pipeline register "ALUout1" posto in MEM/WB. Tale condizione risulta vera se le due istruzioni ALU sono contemporaneamente presenti in EX e WB e se è vera [(ID/EX.Rs1 = MEM/WB.Rd)) or (ID/EX.Rs2 = MEM/WB.Rd)].

1.4) (2 punti) Diagramma clock/stadi in presenza di FU

| SUB R5, R7, R9  |

|-----------------|

| SUB R4, R6, R8  |

| AND R1, R11, R5 |

| ck1 | ck2 | ck3 | ck4 | ck5        | ck6 | ck7 |

|-----|-----|-----|-----|------------|-----|-----|

| IF  | ID  | EX  | MEM | ₩B         |     |     |

|     | IF  | ID  | EX  | MEM        | WB  |     |

|     |     | IF  | ID  | <b>▼EX</b> | MEM | WB  |

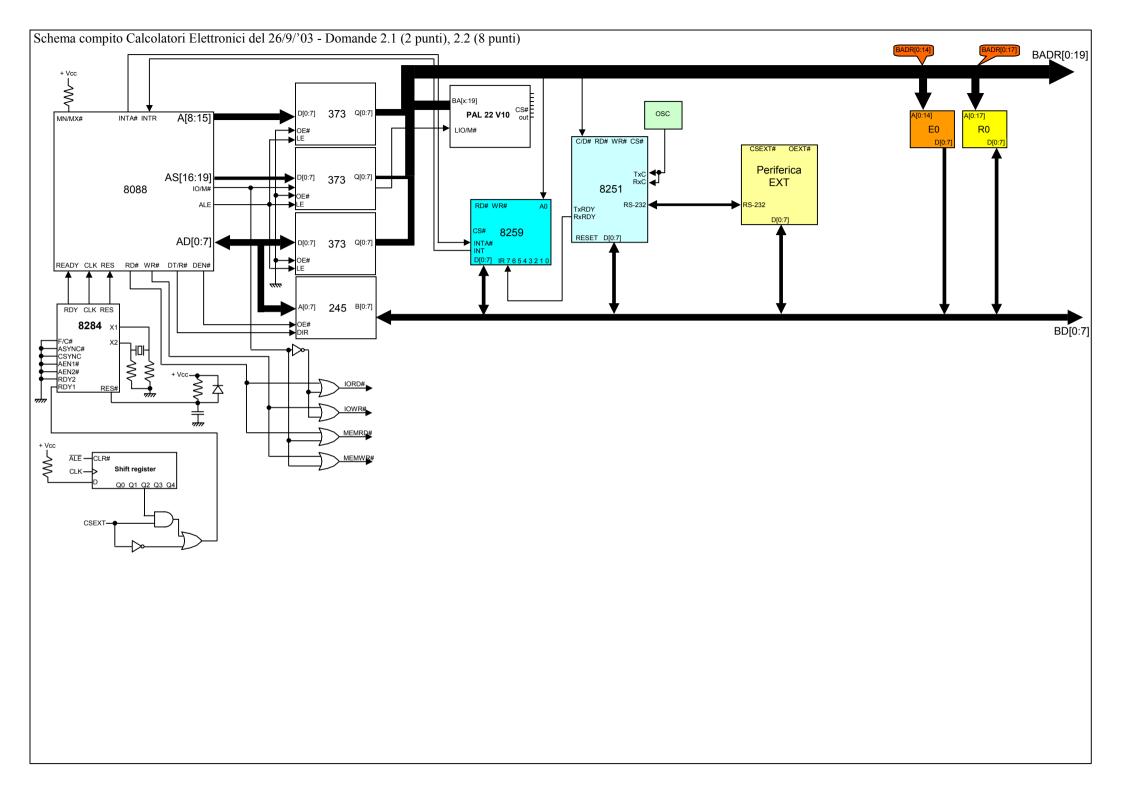

- 2.1) (2 punti) Vedere lo schema per il circuito del ready

- **2.2)** (8 punti) Vedere lo schema per l'interfacciamento.

La frequenza con cui EXT invia i caratteri 55H è bassa al punto da rendere conveniente una gestione ad interrupt dell'interfaccia seriale 8251. Ogni volta che l'8251 ha un carattere per il  $\mu$ P, richiede il servizio di un interrupt ed il  $\mu$ P manda in esecuzione la relativa routine di servizio. All'interno della routine il codice esegue la lettura da seriale e verifica il contenuto del carattere: se questo è 55H essa riabilita le interruzioni con STI consentendo il nesting degli interrupt in attesa dello 0FH, poi inizia le letture indirizzando la periferica EXT con delle IN finché non viene a sua volta interrotta dalla ricezione di 0FH che provoca l'uscita dalle due routine di servizio annidate.

**2.2)** (2 punti) Espressioni di selezione semplificate delle periferiche e delle memorie:

$CS8259 = BA15 \cdot IO/M\#$

$CSE0 = BA19 \cdot !IO/M#$

$CS8251 = !BA15 \cdot !BA14 \cdot IO/M#$

$CSR0 = !BA19 \cdot !IO/M#$

$CSEXT = !BA15 \cdot BA14 \cdot IO/M#$

- 3.1) (3 punti) Affinché un'interfaccia seriale 8251 sia in grado di scambiare dati tra il  $\mu P$  e l'esterno è necessario che, dopo aver fornito tensione, si sia attivato l'ingresso di RESET e successivamente che siano state scritte le due parole di programmazione "mode instruction" e "command instruction".

- **3.2)** (4 punti) Nell'iA16 su 8088 è possibile indirizzare 64K segmenti nello spazio di memoria, tuttavia per gli ultimi 4K segmenti non è possibile indirizzare tutti i 64K offset, cioè vi sono 4096 segmenti con capacità ridotta. A mano a mano che cresce la base di tali segmenti, vengono a mancare multipli di 16 celle, fino ad arrivare all'ultimo segmento per il quale è possibile indirizzare solo 16 celle.

- **3.3)** (2 punti) L'ISA iA16 non consente operazioni tra due operandi in memoria ma, al più, tra un operando registro (o immediato) e uno in memoria e per questo si definisce una macchina M-R (Memory-Register).